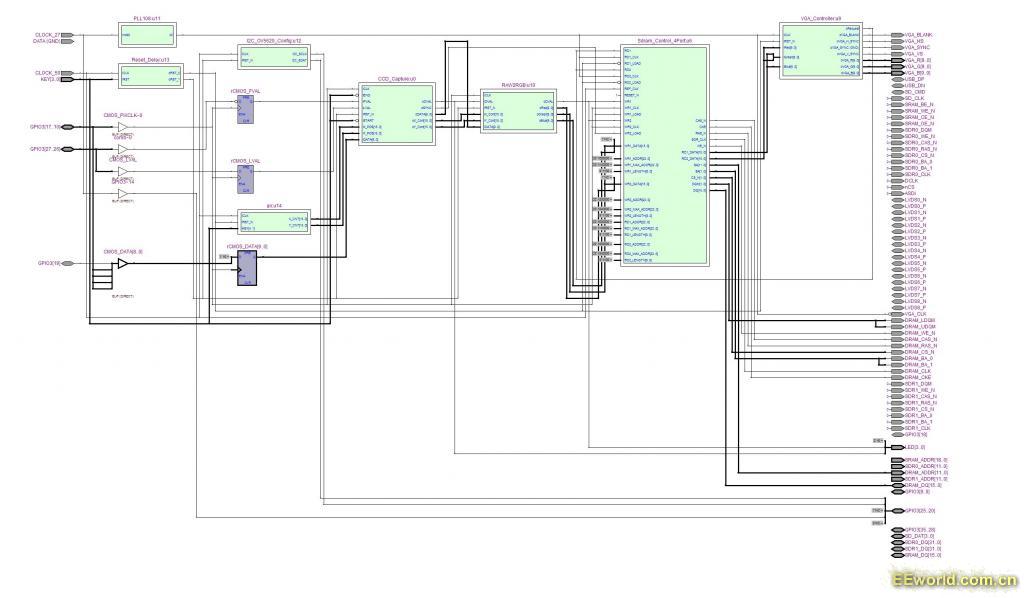

module PIC_LAY (

//////////////////// Clock Input ////////////////////

CLOCK_27, // 27 MHz

CLOCK_50, // 50 MHz

//////////////////// Push Button ////////////////////

KEY, // Pushbutton[3:0]

//////////////////////// LED ////////////////////////

LED, // LED Green[8:0]

//////////////////////// USB ////////////////////////

USB_DP, // USB

USB_DN, // USB

//////////////////// SD_Card Interface ////////////////

SD_DAT, // SD Card Data

SD_CMD, // SD Card Command Signal

SD_CLK, // SD Card Clock

//////////////////// SRAM Interface ////////////////

SRAM_DQ, // SRAM Data bus 16 Bits

SRAM_ADDR, // SRAM Address bus 18 Bits

SRAM_BE_N, // SRAM High-byte Data Mask

SRAM_WE_N, // SRAM Write Enable

SRAM_CE_N, // SRAM Chip Enable

SRAM_OE_N, // SRAM Output Enable

///////////////////// SSDR1 Interface ////////////////

SDR0_DQ, // SSDR Data bus 16 Bits

SDR0_ADDR, // SSDR Address bus 12 Bits

SDR0_DQM, // SSDR Low-byte Data Mask

SDR0_WE_N, // SSDR Write Enable

SDR0_CAS_N, // SSDR Column Address Strobe

SDR0_RAS_N, // SSDR Row Address Strobe

SDR0_CS_N, // SSDR Chip Select

SDR0_BA_0, // SSDR Bank Address 0

SDR0_BA_1, // SSDR Bank Address 0

SDR0_CLK, // SSDR Clock

// SDR0_CKE, // SSDR Clock Enable

///////////////// EPCS FLASH Interface ////////////////////////

DCLK, // SD Card Data

nCS, // SD Card Data 3

ASDI, // SD Card Command Signal

DATA, // SD Card Clock

///////////////// LVDS Interface ////////////////////////

LVDS0_N,LVDS0_P,

LVDS1_N,LVDS1_P,

LVDS2_N,LVDS2_P,

LVDS3_N,LVDS3_P,

LVDS4_N,LVDS4_P,

LVDS5_N,LVDS5_P,

LVDS6_N,LVDS6_P,

LVDS7_N,LVDS7_P,

LVDS8_N,LVDS8_P,

//////////////////// VGA ////////////////////////////

VGA_CLK, // VGA Clock

VGA_HS, // VGA H_SYNC

VGA_VS, // VGA V_SYNC

VGA_BLANK, // VGA BLANK

VGA_SYNC, // VGA SYNC

VGA_R, // VGA Red[9:0]

VGA_G, // VGA Green[9:0]

VGA_B, // VGA Blue[9:0]

///////////////////// SDRAM Interface ////////////////

DRAM_DQ, // SDRAM Data bus 16 Bits

DRAM_ADDR, // SDRAM Address bus 12 Bits

DRAM_LDQM, // SDRAM Low-byte Data Mask

DRAM_UDQM, // SDRAM High-byte Data Mask

DRAM_WE_N, // SDRAM Write Enable

DRAM_CAS_N, // SDRAM Column Address Strobe

DRAM_RAS_N, // SDRAM Row Address Strobe

DRAM_CS_N, // SDRAM Chip Select

DRAM_BA_0, // SDRAM Bank Address 0

DRAM_BA_1, // SDRAM Bank Address 0

DRAM_CLK, // SDRAM Clock

DRAM_CKE, // SDRAM Clock Enable

///////////////////// SSDR1 Interface ////////////////

SDR1_DQ, // SSDR Data bus 16 Bits

SDR1_ADDR, // SSDR Address bus 12 Bits

SDR1_DQM, // SSDR Low-byte Data Mask

SDR1_WE_N, // SSDR Write Enable

SDR1_CAS_N, // SSDR Column Address Strobe

SDR1_RAS_N, // SSDR Row Address Strobe

SDR1_CS_N, // SSDR Chip Select

SDR1_BA_0, // SSDR Bank Address 0

SDR1_BA_1, // SSDR Bank Address 0

SDR1_CLK, // SSDR Clock

// SDR1_CKE, // SSDR Clock Enable

//////////////////// GPIO ////////////////////////////

//GPIO0, // GPIO Connection 0

//GPIO_1, // GPIO Connection 0

//GPIO2, // GPIO Connection 0

GPIO3 // GPIO Connection 1

);

//////////////////////// Clock Input ////////////////////////

input CLOCK_27; // 27 MHz

input CLOCK_50; // 50 MHz

//////////////////////// Push Button ////////////////////////

input [3:0] KEY; // Pushbutton[3:0]

output [3:0] LED; // LED Green[8:0]

//////////////////////// USB ////////////////////////

inout USB_DP; // USB

inout USB_DN; // USB

//////////////////// SD Card Interface ////////////////////////

inout [3:0] SD_DAT; // SD Card Data

inout SD_CMD; // SD Card Command Signal

output SD_CLK; // SD Card Clock

//////////////////// LVDS Interface /////////////////////////////

inout LVDS0_N,LVDS0_P;

inout LVDS1_N,LVDS1_P;

inout LVDS2_N,LVDS2_P;

inout LVDS3_N,LVDS3_P;

inout LVDS4_N,LVDS4_P;

inout LVDS5_N,LVDS5_P;

inout LVDS6_N,LVDS6_P;

inout LVDS7_N,LVDS7_P;

inout LVDS8_N,LVDS8_P;

//////////////////////// VGA ////////////////////////////

output VGA_CLK; // VGA Clock

output VGA_HS; // VGA H_SYNC

output VGA_VS; // VGA V_SYNC

output VGA_BLANK; // VGA BLANK

output VGA_SYNC; // VGA SYNC

output [9:0] VGA_R; // VGA Red[9:0]

output [9:0] VGA_G; // VGA Green[9:0]

output [9:0] VGA_B; // VGA Blue[9:0]

/////////////////////// SDRAM Interface ////////////////////////

inout [15:0] DRAM_DQ; // SDRAM Data bus 16 Bits

output [11:0] DRAM_ADDR; // SDRAM Address bus 12 Bits

output DRAM_LDQM; // SDRAM Low-byte Data Mask

output DRAM_UDQM; // SDRAM High-byte Data Mask

output DRAM_WE_N; // SDRAM Write Enable

output DRAM_CAS_N; // SDRAM Column Address Strobe

output DRAM_RAS_N; // SDRAM Row Address Strobe

output DRAM_CS_N; // SDRAM Chip Select

output DRAM_BA_0; // SDRAM Bank Address 0

output DRAM_BA_1; // SDRAM Bank Address 0

output DRAM_CLK; // SDRAM Clock

output DRAM_CKE; // SDRAM Clock Enable

//////////////////////// SRAM Interface ////////////////////////

inout [15:0] SRAM_DQ; // SRAM Data bus 16 Bits

output[18:0] SRAM_ADDR; // SRAM Address bus 18 Bits

output SRAM_BE_N; // SRAM Data Mask

output SRAM_WE_N; // SRAM Write Enable

output SRAM_CE_N; // SRAM Chip Enable

output SRAM_OE_N; // SRAM Output Enable

/////////////////////// SSDR1 Interface ////////////////////////

inout [31:0] SDR1_DQ; // SSDR Data bus 32 Bits

output[11:0] SDR1_ADDR; // SSDR Address bus 12 Bits

output SDR1_DQM; // SSDR Data Mask

output SDR1_WE_N; // SSDR Write Enable

output SDR1_CAS_N; // SSDR Column Address Strobe

output SDR1_RAS_N; // SSDR Row Address Strobe

output SDR1_CS_N; // SSDR Chip Select

output SDR1_BA_0; // SSDR Bank Address 0

output SDR1_BA_1; // SSDR Bank Address 0

output SDR1_CLK; // SSDR Clock

//output SDR1_CKE; // SSDR Clock Enable

/////////////////////// SSDR1 Interface ////////////////////////

inout [31:0] SDR0_DQ; // SSDR Data bus 32 Bits

output[11:0] SDR0_ADDR; // SSDR Address bus 12 Bits

output SDR0_DQM; // SSDR Data Mask

output SDR0_WE_N; // SSDR Write Enable

output SDR0_CAS_N; // SSDR Column Address Strobe

output SDR0_RAS_N; // SSDR Row Address Strobe

output SDR0_CS_N; // SSDR Chip Select

output SDR0_BA_0; // SSDR Bank Address 0

output SDR0_BA_1; // SSDR Bank Address 0

output SDR0_CLK; // SSDR Clock

//output SDR0_CKE; // SSDR Clock Enable

//////////////////// EPCS FLASH Interface ////////////////////////

output DCLK; // SD Card Data

output nCS; // SD Card Data 3

output ASDI; // SD Card Command Signal

input DATA; // SD Card Clock

//////////////////////// GPIO ////////////////////////////////

//inout [29:0] GPIO0; // GPIO Connection 0

//inout [29:0] GPIO1; // GPIO Connection 0

//inout [17:0] GPIO2; // GPIO Connection 1

inout [35:0] GPIO3; // GPIO Connection 1

// CMOS

wire [9:0] CMOS_DATA;

wire CMOS_FVAL;

wire CMOS_LVAL;

wire CMOS_PIXCLK;

reg CMOS_XCLK;

wire [31:0] Read_DATA;

wire VGA_CTRL_CLK;

wire AUD_CTRL_CLK;

wire DLY_RST_0;

wire DLY_RST_1;

wire DLY_RST_2;

wire Read;

reg [9:0] rCMOS_DATA;

reg rCMOS_LVAL;

reg rCMOS_FVAL;

wire SDRAM_BUSY;

wire Image_Read;

wire [31:0]Image_Read_Data;

wire Image_Write;

wire Image_Write_CLK;

wire [31:0]Image_Write_Data;

wire CLOCK_18_4;

reg CLOCK_25;

wire CLOCK_20;

wire CLOCK_65;

wire CLOCK_108;

wire CLOCK_100;

wire CLOCK_125;

// For Sensor OV5620

//assign CMOS_DATA[] = GPIO3[15];

assign CMOS_DATA[0] = GPIO3[10];

assign CMOS_DATA[1] = GPIO3[11];

assign CMOS_DATA[2] = GPIO3[13];

assign CMOS_DATA[3] = GPIO3[12];

assign CMOS_DATA[4] = GPIO3[15];

assign CMOS_DATA[5] = GPIO3[14];

assign CMOS_DATA[6] = GPIO3[17];////////

assign CMOS_DATA[7] = GPIO3[16];

assign CMOS_DATA[8] = GPIO3[19];

assign CMOS_FVAL = ~GPIO3[26];

assign CMOS_LVAL = GPIO3[27];

assign CMOS_PIXCLK = GPIO3[13];

assign GPIO3[22] = CLOCK_27;//CMOS MCLK OUTPUT

always@(posedge CMOS_PIXCLK)

begin

rCMOS_DATA <= CMOS_DATA;

rCMOS_LVAL <= CMOS_LVAL;

rCMOS_FVAL <= CMOS_FVAL;

end

wire [9:0] mCMOS_DATA;

wire mCMOS_DVAL;

wire wSYNC;

wire [15:0] X_Cont;

wire [15:0] Y_Cont;

wire [15:0] TX_Cont;

wire [15:0] TY_Cont;

wire [31:0] Frame_Cont;

CCD_Capture u0 (

.iCLK (CMOS_PIXCLK),

.iRST_N (DLY_RST_1),

.iDATA (rCMOS_DATA),

.iFVAL (rCMOS_FVAL),

.iLVAL (rCMOS_LVAL),

.iSTART (!KEY[3]),

.iEND (!KEY[2]),

.iX_POS (X_POS),//

.iY_POS (Y_POS),//

.oDATA (mCMOS_DATA),

.oDVAL (mCMOS_DVAL),

.oX_Cont (X_Cont),

.oY_Cont (Y_Cont),

.oTX_Cont (TX_Cont),

.oSYNC (wSYNC),

.oTY_Cont (TY_Cont),

.oFrame_Cont (Frame_Cont)

);

wire mCMOS_DVAL_d;

RAW2RGB u10 (

.iX_Cont (X_Cont),

.iY_Cont (Y_Cont),

.iDATA (mCMOS_DATA),

.iDVAL (mCMOS_DVAL),

.oRed (mCMOS_R),

.oGreen (mCMOS_G),

.oBlue (mCMOS_B),

.oDVAL (mCMOS_DVAL_d),

.iCLK (CMOS_PIXCLK),

.iRST_N (DLY_RST_1)

);

wire [9:0] mCMOS_R,mCMOS_G,mCMOS_B;

assign LED[0] = mCMOS_DVAL;

assign LED[1] = mCMOS_DVAL_d;

//VGA_OUT_BUFFER

/*Sdram_Control_4Port u8 ( // HOST Side

.REF_CLK(CLOCK_50),

.RESET_N(1'b1),

.CLK_100OUT(CLOCK_100),

// FIFO Write Side 1

.WR1_DATA ({mCMOS_R,mCMOS_G,mCMOS_B}),

.WR1 (mCMOS_DVAL_d),

.WR1_ADDR (0),

.WR1_MAX_ADDR (1280*1024),

.WR1_LENGTH (9'h100),

.WR1_LOAD (wSYNC),

.WR1_CLK (CMOS_PIXCLK),

// FIFO Read Side 1

.RD1_DATA ({Image_Read_R,Image_Read_G,Image_Read_B}),

.RD1 (VGA_Read_Req),

.RD1_ADDR (0),

.RD1_MAX_ADDR (1280*1024),

.RD1_LENGTH (9'h100),

.RD1_LOAD (!DLY_RST_0),

.RD1_CLK (VGA_CTRL_CLK),

// SDRAM Side

.SA (SDR0_ADDR),

.BA ({SDR0_BA_1,SDR0_BA_0}),

.CS_N (SDR0_CS_N),

.RAS_N (SDR0_RAS_N),

.CAS_N (SDR0_CAS_N),

.WE_N (SDR0_WE_N),

.DQ (SDR0_DQ),

.DQM (SDR0_DQM)

,.SDR_CLK (SDR_CLK)

);

*/

Sdram_Control_4Port u6 ( // HOST Side

.REF_CLK(CLOCK_50),

.RESET_N(1'b1),

//.CLK_100OUT(CLOCK_100),

// FIFO Write Side 1

.WR1_DATA( {mCMOS_G[9:5],

mCMOS_B[9:0]}),

.WR1(mCMOS_DVAL_d),

.WR1_ADDR(0),

.WR1_MAX_ADDR(1280*1024),

.WR1_LENGTH(9'h100),

.WR1_LOAD(wSYNC),

.WR1_CLK(CMOS_PIXCLK),

// FIFO Write Side 2

.WR2_DATA( {mCMOS_G[4:0],

mCMOS_R[9:0]}),

.WR2(mCMOS_DVAL_d),

.WR2_ADDR(22'h200000),

.WR2_MAX_ADDR(22'h200000+1280*1024),

.WR2_LENGTH(9'h100),

.WR2_LOAD(wSYNC),

.WR2_CLK(CMOS_PIXCLK),

// FIFO Read Side 1

.RD1_DATA({Image_Read_G[9:5],

Image_Read_B[9:0]}),

.RD1(VGA_Read_Req),

.RD1_ADDR(0),

.RD1_MAX_ADDR(1280*1024),

.RD1_LENGTH(9'h100),

.RD1_LOAD(!DLY_RST_0),

.RD1_CLK(VGA_CTRL_CLK),

// FIFO Read Side 2

.RD2_DATA({Image_Read_G[4:0],

Image_Read_R[9:0]}),

.RD2(VGA_Read_Req),

.RD2_ADDR(22'h200000),

.RD2_MAX_ADDR(22'h200000+1280*1024),

.RD2_LENGTH(9'h100),

.RD2_LOAD(!DLY_RST_0),

.RD2_CLK(VGA_CTRL_CLK),

// SDRAM Side

.SA(DRAM_ADDR),

.BA({DRAM_BA_1,DRAM_BA_0}),

.CS_N(DRAM_CS_N),

.CKE(DRAM_CKE),

.RAS_N(DRAM_RAS_N),

.CAS_N(DRAM_CAS_N),

.WE_N(DRAM_WE_N),

.DQ(DRAM_DQ),

.DQM({DRAM_UDQM,DRAM_LDQM}),

.SDR_CLK(SDR_CLK)

//.VGA_CLK_TO_C2(VGA_CTRL_CLK)

);

assign DRAM_CLK = SDR_CLK;

//assign SDR1_CLK = SDR_CLK;

wire VGA_Read_Req;

//VGA_VS;

wire [9:0] Image_Read_R;

wire [9:0] Image_Read_G;

wire [9:0] Image_Read_B;

//assign GPIO0[27] = VGA_CTRL_CLK;

//assign GPIO0[28] = VGA_VS;

assign VGA_CLK = ~VGA_CTRL_CLK;

VGA_Controller u9( // Host Side

.iRed (Image_Read_R),

.iGreen (Image_Read_G),

.iBlue (Image_Read_B),

.oRequest (VGA_Read_Req),

/*

// VGA Side

.oVGA_R ({GPIO1[21],GPIO1[20],GPIO1[23],GPIO1[22],GPIO1[25],

GPIO1[24],GPIO1[27],GPIO1[26],GPIO1[29],GPIO1[28]}),

.oVGA_G (GPIO0[15:6]),

.oVGA_B (GPIO0[26:17]),

.oVGA_H_SYNC (GPIO0[29]),

.oVGA_V_SYNC (VGA_VS),

.oVGA_BLANK (GPIO0[16]),

*/

// VGA Side

.oVGA_R(VGA_R),

.oVGA_G(VGA_G),

.oVGA_B(VGA_B),

.oVGA_H_SYNC(VGA_HS),

.oVGA_V_SYNC(VGA_VS),

.oVGA_SYNC(VGA_SYNC),

.oVGA_BLANK(VGA_BLANK),

// Control Signal

.iCLK(VGA_CTRL_CLK),

.iRST_N(DLY_RST_0)

)

;

I2C_OV5620_Config u12(

.iCLK(CLOCK_50),

.iRST_N(DLY_RST_1),

// I2C Side

.I2C_SCLK(GPIO3[24]),

.I2C_SDAT(GPIO3[25])

);

PLL108 u11(

.inclk0 (CLOCK_27),

.c0 (VGA_CTRL_CLK)

);

Reset_Delay u13(

.iCLK (CLOCK_50),

.iRST (KEY[0]),

.oRST_0 (DLY_RST_0),

.oRST_1 (DLY_RST_1),

.oRST_2 (DLY_RST_2)

);

wire [15:0] X_POS,Y_POS;

an u14(

.iCLK (CLOCK_50),

.iRST_N (DLY_RST_0),

.iKEY (KEY[3:0]),

.X_CNT (X_POS),

.Y_CNT (Y_POS) );

endmodule

1/6

1/6

1/6

1/6

京公网安备 11010802033920号

Copyright © 2005-2025 EEWORLD.com.cn, Inc. All rights reserved

京公网安备 11010802033920号

Copyright © 2005-2025 EEWORLD.com.cn, Inc. All rights reserved

京公网安备 11010802033920号

Copyright © 2005-2025 EEWORLD.com.cn, Inc. All rights reserved

京公网安备 11010802033920号

Copyright © 2005-2025 EEWORLD.com.cn, Inc. All rights reserved

提升卡

提升卡 变色卡

变色卡 千斤顶

千斤顶