|

通过串联或并联电容、电感的方法可以是传输线的容差和电抗发生改变,阻抗匹配器件会影响功率水平,并且需要使用额定电压水平更高的器件来优化天线效率。下面看一下Qorvo的方法。

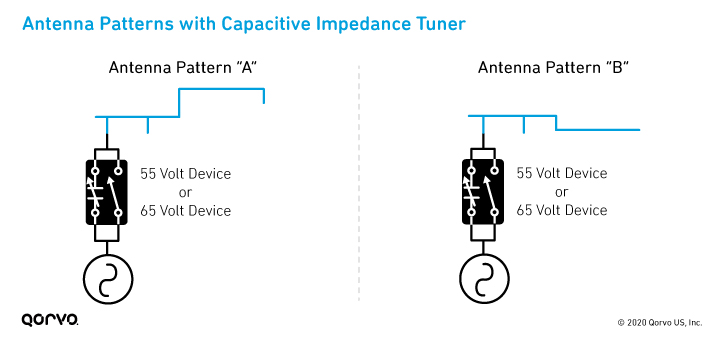

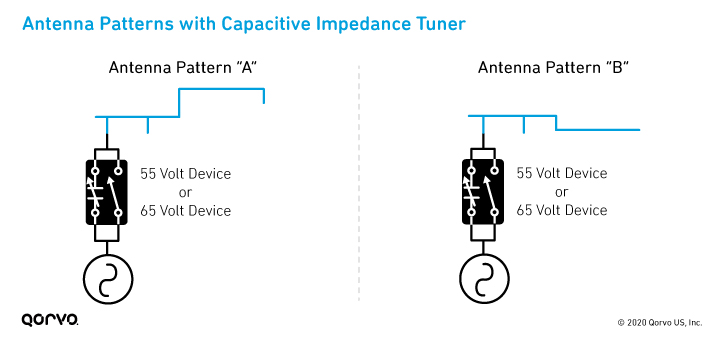

图 2 为两种天线设计,即模式 A 和 B。接下来,我们将阐述这些设计模式与不同额定电压的阻抗匹配组件会如何相互影响。我们还将介绍如何利用额定电压更高的器件来最大程度地提高总辐射效率。

Figure 2

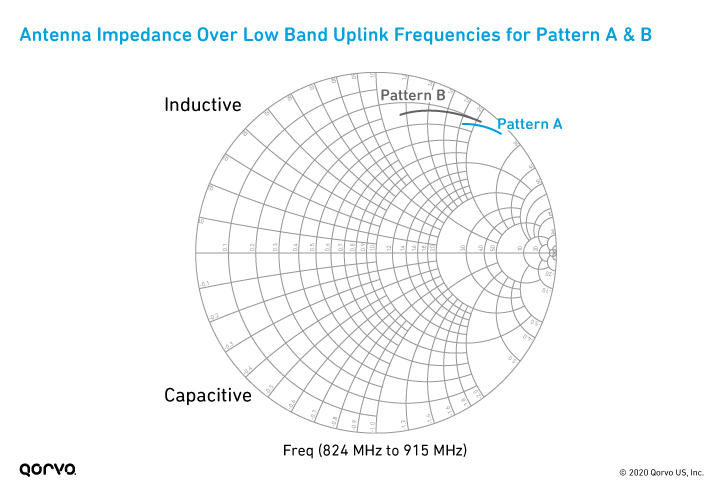

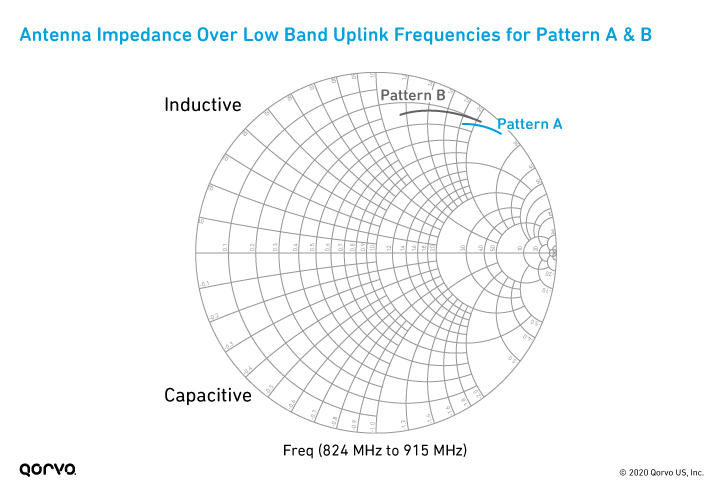

首先,在图 3 中我们可以看到,天线模式“A”和“B”在史密斯圆图上如何通过低频段 GSM 频率进行测量。如图所示,天线阻抗位于史密斯圆图的电感区域,因此串联电容成为最优匹配解决方案。因此,我们的天线匹配解决方案将使用电容。

Figure 3.

在我们的示例中,我们将图 4 左侧所示的两个类似器件作为天线阻抗匹配组件进行了测量和比较。一个是 55VRF (DEVICE55),另一个是 65VRF (DEVICE65)。每个器件都由具有 32 种不同电容状态的可编程电容和独立的可切换开关组成。

Figure 4.

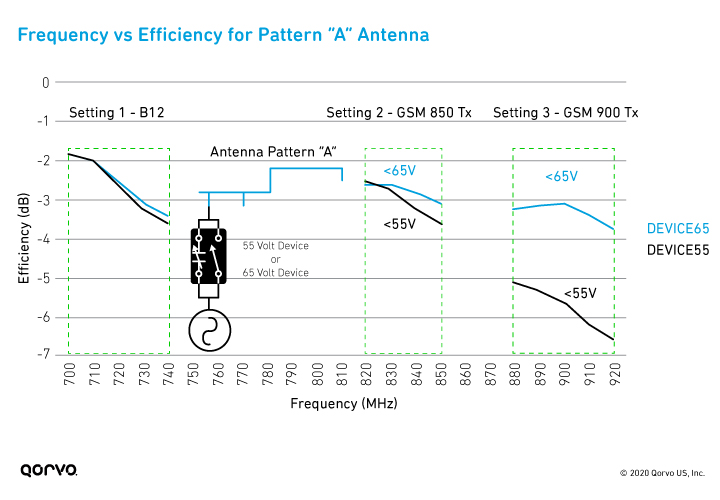

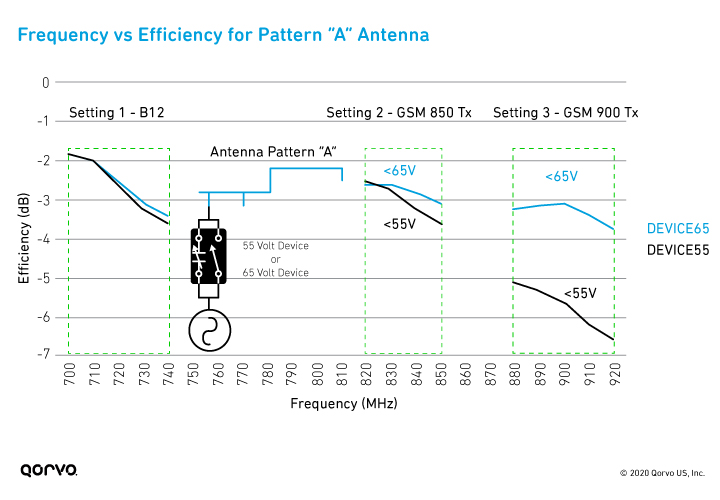

通过选择每个器件的状态,使天线模式 A 在低频段频率范围内实现最大辐射效率。此外,所选的器件状态还应符合每个器件的额定射频电压要求:DEVICE55 为 55VRF,DEVICE65 为 65VRF,如下图所示。器件在 GSM850/900 和 LTE B12(频段 12)下进行了测试。测量图(下图 5)为连接这两个器件的天线效率与频率图。

Figure 5.

上述输出测量采用了 DEVICE 55 和 DEVICE 65 的天线模式“A”。如图所示,如果使用电压较低的 55 V 器件,在 GSM850 和 GSM900 Tx 频率下,效率会受到明显影响。为了在 GSM850、GSM900 以及 B12 下实现更高的效率,同时保持电压电平,应选择 DEVICE65 的电压,因为其效率会超过 DEVICE55。

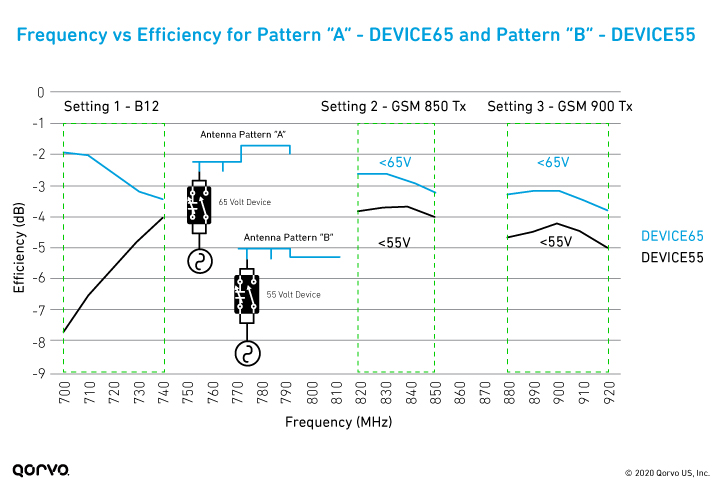

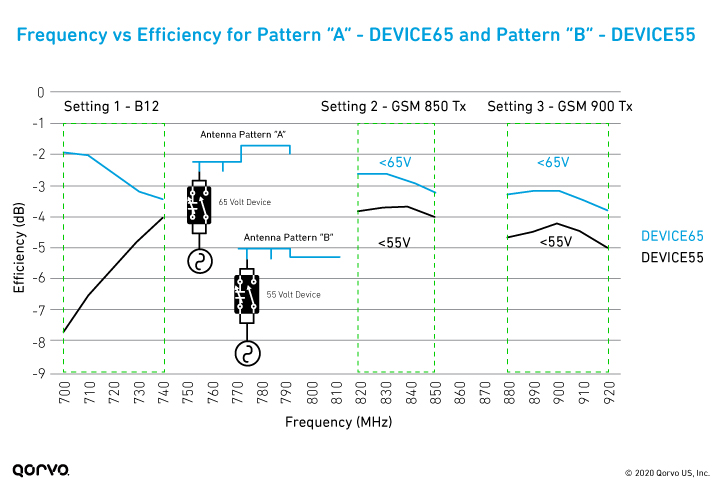

为提高 DEVICE55 响应性能,我们尝试使用模式“B”天线设计。下述输出测量图显示了使用 DEVICE65 的模式“A”。对于 DEVICE55,我们使用了模式“B”。尽管在 GSM 频率下使用模式“B”天线设计可以改进 DEVICE55 方案的效果,但仍不足以达到 DEVICE65 组件的要求。如图 6 中所示,DEVICE65 的效率再一次超过了 DEVICE55。因为 DEVICE65 能够满足较高的射频电压输入阻抗要求。

Figure 6.

此外,使用模式“B”和 DEVICE55 所实现的效率没有使用模式“A”和 DEVICE65 的那么高,频段也没有那么宽,尤其是在 B12 频率范围内。尽管使用模式“B”时,DEVICE55 会有所改进,但效率没有使用模式“A”和 DEVICE65 那么高。

总之,天线上的高电压的确会对效率和性能产生影响。我们的测量结果证实,在高射频电压的阻抗匹配应用中,额定电压更高的器件可实现更高的性能。在我们的示例中,我们采用 Qorvo 的两款可配置调谐器,每款调谐器都包含一个开关和一个可编程电容阵列 (PAC) ,一个器件的额定电压为 55V,另一个为 65V。额定电压更高的组件可为天线设计人员提供更多的裕量。从而使系统设计人员能够在不修改设计布局结构的情况下,更有效地将电路与多个天线模式和射频电压情境进行匹配。

哪种阻抗匹配方法好呢?大家一下来讨论一下呢?

|

提升卡

提升卡 变色卡

变色卡 千斤顶

千斤顶 你说的太到位了,可以说是秒懂阻抗匹配了,谢谢。

你说的太到位了,可以说是秒懂阻抗匹配了,谢谢。