|

去耦电容的选择、容值计算和pcb布局布线详解

国科环宇 • 2018-01-28 18:28 • 7229次阅读

去耦电容的应用的非常广泛,在电路应用过程中对于去耦电容的容值计算和PCB电路布局布线有一些我们必须要了解的技巧。

有源器件在开关时产生的高频开关噪声将沿着电源线传播。去耦电容的主要功能就是提供一个局部的直流电源给有源器件,以减少开关噪声在板上的传播,和将噪声引导到地。

去耦电容的容值计算

去耦的初衷是:不论IC对电流波动的规定和要求如何都要使电压限值维持在规定的允许误差范围之内。 使用表达式:

C⊿U=I⊿t

由此可计算出一个IC所要求的去耦电容的电容量C。

⊿U是实际电源总线电压所允许的降低,单位为V。

I是以A(安培)为单位的最大要求电流;

⊿t是这个要求所维持的时间。

去耦电容容值计算方法: 推荐使用远大于1/m乘以等效开路电容的电容值。

此处m是在IC的电源插针上所允许的电源总线电压变化的最大百分数,一般IC的数据手册都会给出具体的参数值。

等效开路电容定义为:

C=P/(fU^2) 式中:

P——IC所耗散的总瓦数;

U——IC的最大DC供电电压;

f——IC的时钟频率。

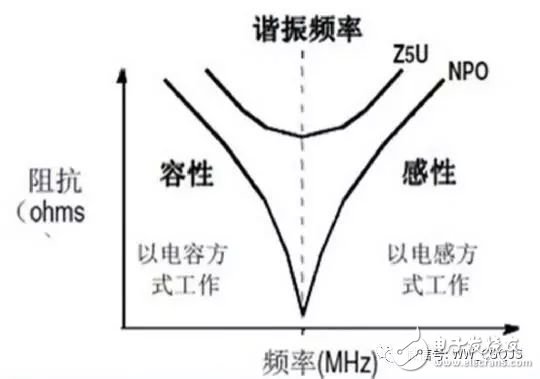

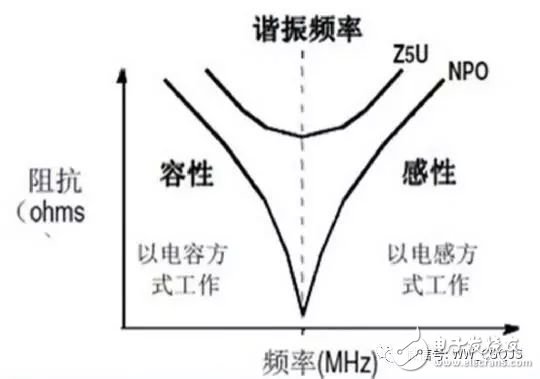

电容的容值选择一般取决于电容的谐振频率。

不同封装的电容有不同的谐振频率,下表列出了不同容值不同封装的电容的谐振频率:

需要注意的是数字电路的去耦,低的ESR值比谐振频率更为重要,因为低的ESR值可以提供更低阻抗的到地通路,这样当超过谐振频率 的电容呈现感性时仍能提供足够的去耦能力。

降低去耦电容ESL的方法

去耦电容的ESL是由于内部流动的电流引起的,使用多个去耦电容并联的方式可以降低电容的ESL影响,而且将两个去耦电容以相反走向放置在一起,从 而使它们的内部电流引起的磁通量相互抵消,能进一步降低ESL。(此方法适用于任何数目的去耦电容,注意不要侵犯DELL公司的专利)

IC去耦电容的数目选择

在设计原理图的时候,经常遇到的问题是为芯片的电源引脚设计去耦电容,上面已经介绍了去耦电容的容值选择,但是数目选择怎么确定呢?理论上是每个电 源引脚最好分配一个去耦电容,但是在实际情况中,却经常看到去耦电容的数目要少于电源引脚数目的情况,如freescale提供的iMX233的PDK原 理图中,内存SDRAM有15个电源引脚,但是去耦电容的数目是10个。

去耦电容数目选择依据

在布局空间允许的情况下,最好做到一个电源引脚分配一个去耦电容,但是在空间不足的时候,可以适当削减电容的数目,具体情况应该根据芯片上电源引脚 的具体分布决定,因为厂家在设计IC的时候,经常是几个电源引脚在一起,这样可以共用去耦电容,减少去耦电容的数目。

电容的安装方法 电容的摆放

对于电容的安装,首先要提到的就是安装距离。容值最小的电容,有最高的谐振频率,去耦半径最小,因此放在最靠近芯片的位置。容值稍大些的可以距离稍 远,最外层放置容值最大的。但是,所有对该芯片去耦的电容都尽量靠近芯片。另外的一个原因是:如果去耦电容离IC电源引脚较远,则布线阻抗将减小去耦电容 的效力。

还有一点要注意,在放置时,最好均匀分布在芯片的四周,对每一个容值等级都要这样。通常芯片在设计的时候就考虑到了电源和地引脚的排列位置,一般都 是均匀分布在芯片的四个边上的。因此,电压扰动在芯片的四周都存在,去耦也必须对整个芯片所在区域均匀去耦。

电容的安装

在安装电容时,要从焊盘拉出一小段引出线,然后通过过孔和电源平面连接,接地端也是同样。放置过孔的基本原则就是让这一环路面积最小,进而使总的寄 生电感最小。图16显示了几种过孔放置方法。

第一种方法从焊盘引出很长的引出线然后连接过孔,这会引入很大的寄生电感,一定要避免这样做,这时最糟糕的安装方式。

第二种方法在焊盘的两个端点紧邻焊盘打孔,比第一种方法路面积小得多,寄生电感也较小,可以接受。

第三种在焊盘侧面打孔,进一步减小了回路面积,寄生电感比第二种更小,是比较好的方法。

第四种在焊盘两侧都打孔,和第三种方法相比,相当于电容每一端都是通过过孔的并联接入电源平面和地平面,比第三种寄生电感更小,只要空间允许,尽量 用这种方法。

最后一种方法在焊盘上直接打孔,寄生电感最小,但是焊接是可能会出现问题,是否使用要看加工能力和方式。 推荐使用第三种和第四种方法。

需要强调一点:有些工程师为了节省空间,有时让多个电容使用公共过孔。任何情况下都不要这样做。最好想办法优化电容组合的设计,减少电容数量。 由于印制线越宽,电感越小,从焊盘到过孔的引出线尽量加宽,如果可能,尽量和焊盘宽度相同。这样即使是0402封装的电容,你也可以使用20mil 宽的引出线。引出线和过孔安装如图17所示,注意图中的各种尺寸。

对于大尺寸的电容,比如板级滤波所用的钽电容,推荐用图18中的安装方法。注意:小尺寸电容禁止在两个焊盘间打孔,因为容易引起短 路。

电容的去耦半径

对于大尺寸的电容,比如板级滤波所用的钽电容,推荐用图18中的安装方法。注意:小尺寸电容禁止在两个焊盘间打孔,因为容易引起短路。

电容的去耦半径

电容去耦的一个重要问题是电容的去耦半径。大多数资料中都会提到电容摆放要尽量靠近芯片,多数资料都是从减小回路电感的角度来谈这个摆放距离问题。 确实,减小电感是一个重要原因,但是还有一个重要的原因大多数资料都没有提及,那就是电容去耦半径问题。如果电容摆放离芯片过远,超出了它的去耦半径,电 容将失去它的去耦的作用。

理解去耦半径最好的办法就是考察噪声源和电容补偿电流之间的相位关系。当芯片对电流的需求发生变化时,会在电源平面的一个很小的局部区域内产生电压 扰动,电容要补偿这一电流(或电压),就必须先感知到这个电压扰动。信号在介质中传播需要一定的时间,因此从发生局部电压扰动到电容感知到这一扰动之间有 一个时间延迟。同样,电容的补偿电流到达扰动区也需要一个延迟。因此必然造成噪声源和电容补偿电流之间的相位上的不一致。

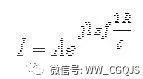

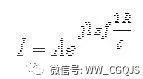

特定的电容,对与它自谐振频率相同的噪声补偿效果最好,我们以这个频率来衡量这种相位关系。设自谐振频率为f,对应波长为λ,补偿电流表达式可写 为:

其中,A是电流幅度,R为需要补偿的区域到电容的距离,C为信号传播速度。 当扰动区到电容的距离达到λ/4时,补偿电流的相位为π,和噪声源相位刚好差180度,即完全反相。此时补偿电流不再起作用,去耦作用失效,补偿的 能量无法及时送达。为了能有效传递补偿能量,应使噪声源和补偿电流的相位差尽可能的小,最好是同相位的。距离越近,相位差越小,补偿能量传递越多,如果距 离为0,则补偿能量百分之百传递到扰动区。这就要求噪声源距离电容尽可能的近,要远小于λ/4。实际应用中,这一距离最好控制在λ/40-λ/50之间, 这是一个经验数据。

例如:0.001uF陶瓷电容,如果安装到电路板上后总的寄生电感为1.6nH,那么其安装后的谐振频率为125.8MHz,谐振周期为 7.95ps。假设信号在电路板上的传播速度为166ps/inch,则波长为47.9英寸。电容去耦半径为47.9/50=0.958英寸,大约等于 2.4厘米。 本例中的电容只能对它周围2.4厘米范围内的电源噪声进行补偿,即它的去耦半径2.4厘米。不同的电容,谐振频率不同,去耦半径也不同。对于大电 容,因为其谐振频率很低,对应的波长非常长,因而去耦半径很大,这也是为什么我们不太关注大电容在电路板上放置位置的原因。对于小电容,因去耦半径很小, 应尽可能的靠近需要去耦的芯片,这正是大多数资料上都会反复强调的,小电容要尽可能近的靠近芯片放置。

综上所述,在选择去耦电容时,需要考虑的因素有电容的ESR、ESL值,谐振频率,布局时要注意根据IC电源引脚的数目和周围布局 空间决定去耦电容数目,根据去耦半径决定具体的布局位置。

|  1/6

1/6

京公网安备 11010802033920号

Copyright © 2005-2025 EEWORLD.com.cn, Inc. All rights reserved

京公网安备 11010802033920号

Copyright © 2005-2025 EEWORLD.com.cn, Inc. All rights reserved

提升卡

提升卡 变色卡

变色卡 千斤顶

千斤顶