|

ARM 有7个基本工作模式

User : 非特权模式,大部分任务执行在这种模式

FIQ : 当一个高优先级(fast) 中断产生时将会进入这种模式

IRQ : 当一个低优先级(normal) 中断产生时将会进入这种模式

Supervisor :当复位或软中断指令执行时将会进入这种模式

Abort : 当存取异常时将会进入这种模式

Undef : 当执行未定义指令时会进入这种模式

System : 使用和User模式相同寄存器集的特权模式

注意:除User(用户模式)是Normal(普通模式)外,其他6种都是Privilege(特权模式)。 Privilege中除Sys模式外,其余5种为异常模式。 各种模式的切换,可以是程序员通过代码主动切换(通过写CPSR寄存器);也可以是CPU在某些情况下自动切换。 各种模式下权限和可以访问的寄存器不同。

非特权模式:User

特权模式:

异常模式:FIQ IRQ Svc Abort Udef

非异常模式:System Monitor

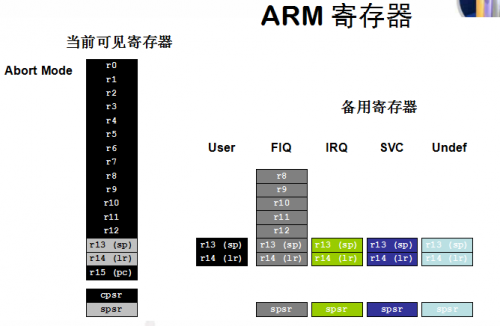

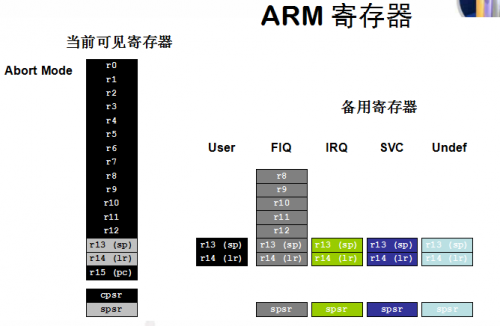

ARM寄存器分析

ARM共有37个寄存器,都是32位长度 37个寄存器中30个为“通用”型,1个固定用作PC,一个固定用作CPSR,5个固定用作5种异常模式下的SPSR。

r13(sp)用作堆栈可以保存上下文,便于以后跳转回来能继续执行

r14(lr)用于存储返回地址,当我们返回原模式可以bl lr或者mov pc lr这样就实现了返回

r15(pc):程序指针,PC指向哪里,CPU就会执行哪条指令(所以程序跳转时就是把目标地址代码放到PC中)

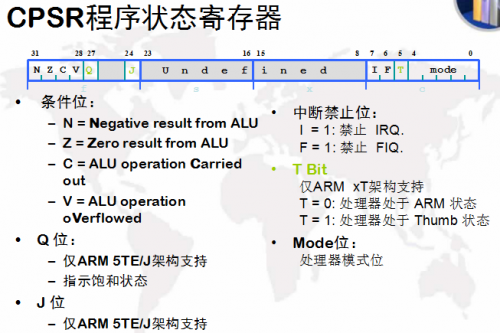

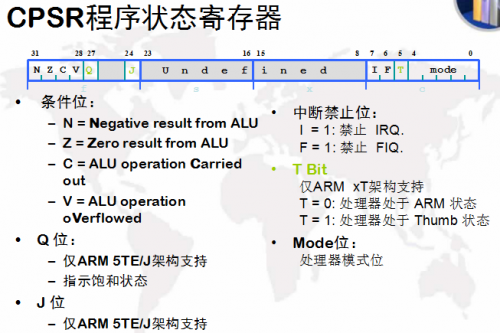

cpsr:中各个bit位表明了cpu的某些状态信息,这些信息非常重要,和后面学到的汇编指令息息相关(譬如BLE指令中的E就和

CPSR中的Z标志位有关) cpsr中的I、F位和开中断、关中断有关 cpsr中的mode位(bit4~bit0共5位)决定了CPU的工作模式,

在uboot代码中会使用汇编进行设置。

spsr:用来保存cpsr

1.条件标志位

-N: Negative result from ALU

-Z: Zero result from ALU

-C: ALU operation Carried out (进位/借位)

-V: ALU operation overflowed (溢出)

* N=1时,说明运算的结果为负数,N=0时,说明运算的结果为正数或零。

* Z=1时,说明运算的结果为0,Z=0时,说明运算的结果为非0。

* C:

- 加法运算(包括CMP):当运算结果产生了进位时(无符号数溢出),C=1,否则为0。

- 减法运算(包括CMP):当运算结果产生了借位时(无符号数溢出),C=0,否则C=1。

- 对于包含移位操作的非加减指令操作时,C为移除值的最后一位。

- 对于其它的非加减指令,C的值通常不变。

* V:

- 对于加减法运算指令,当操作数和运算结果为二进制的补码表示的带符号数时,V=1表示符号位溢出

- 对于其它的非加减法指令,V的值通常不变。

2.Q位:

* 在ARM V5及以上的版本的E系列处理器中,Q标识位指示增强的DSP运算指令是否发生了溢出,在其它版本的处理器中,Q未定义。

3.J位:

* 仅ARM 5TE/J 架构支持

* J=1时,处理器处于Jazelle状态

跳转过程

异常向量表

所有的CPU都有异常向量表,这是CPU设计时就设定好的,是硬件决定的。 当异常发生时,CPU会自动动作(PC跳转到异常向量处处理异常,有时伴有一些辅助动作) 异常向量表是硬件向软件提供的处理异常的支持。

***异常产生时

做好保护现场的工作:

(1)把cpsr保存到spsr中,设置适当的cpsr(改变处理器的ARM状态、改变处理器进入相应的异常模式、(视情况)改变中断禁止位禁止相应中断)

(2)保存返回地址到lr

(3)设置pc为相应的异常向量

实现跳转。

***异常返回时

做好恢复现场工作:

(1)从spsr恢复cpsr

(2)从lr恢复pc

注意:这些操作必须在ARM状态执行

TIPS:

(1)异常向量表中除了FIQ中断都是4个字节,所以只够存放一段异常处理程序的代码的首地址

(2)FIQ中断为快速中断,其中一个特殊的地方就体现在他的异常向量表(Vector Table)地址在最后一个,所以它可以存放不止4个字节,这样的话FIQ中断可以不用只存放地址,而是把整个异常处理程序放进去,这样就少跳转了一次,加快了中断相应速度。

|  1/10

1/10

京公网安备 11010802033920号

Copyright © 2005-2024 EEWORLD.com.cn, Inc. All rights reserved

京公网安备 11010802033920号

Copyright © 2005-2024 EEWORLD.com.cn, Inc. All rights reserved

提升卡

提升卡 变色卡

变色卡 千斤顶

千斤顶